# Characterization of silicon heterojunctions for Solar Cells

Jean-Paul Kleider, José Alvarez, Martin Labrune, Pere Roca I Cabarrocas, Olga Alexandrovna Maslova, Wilfried Favre, Marie-Estelle Gueunier-Farret

## ▶ To cite this version:

Jean-Paul Kleider, José Alvarez, Martin Labrune, Pere Roca I Cabarrocas, Olga Alexandrovna Maslova, et al.. Characterization of silicon heterojunctions for Solar Cells. Nanoscale Research Letters, 2011, 6, pp.152. 10.1186/1556-276X-6-152 . hal-00641696

## HAL Id: hal-00641696 https://polytechnique.hal.science/hal-00641696

Submitted on 16 Nov 2011

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### NANO EXPRESS

**Open Access**

# Characterization of silicon heterojunctions for solar cells

Jean-Paul Kleider<sup>1\*</sup>, Jose Alvarez<sup>1</sup>, Alexander Vitalievitch Ankudinov<sup>2</sup>, Alexander Sergeevitch Gudovskikh<sup>3</sup>, Ekaterina Vladimirovna Gushchina<sup>2</sup>, Martin Labrune<sup>4,5</sup>, Olga Alexandrovna Maslova<sup>1,3</sup>, Wilfried Favre<sup>1</sup>, Marie-Estelle Gueunier-Farret<sup>1</sup>, Pere Roca i Cabarrocas<sup>4</sup>, Eugene Ivanovitch Terukov<sup>2</sup>

#### Abstract

Conductive-probe atomic force microscopy (CP-AFM) measurements reveal the existence of a conductive channel at the interface between *p*-type hydrogenated amorphous silicon (*a*-Si:H) and *n*-type crystalline silicon (*c*-Si) as well as at the interface between *n*-type *a*-Si:H and *p*-type *c*-Si. This is in good agreement with planar conductance measurements that show a large interface conductance. It is demonstrated that these features are related to the existence of a strong inversion layer of holes at the *c*-Si surface of (*p*) *a*-Si:H/(*n*) *c*-Si structures, and to a strong inversion layer of electrons at the *c*-Si surface of (*n*) *a*-Si:H/(*p*) *c*-Si heterojunctions. These are intimately related to the band offsets, which allows us to determine these parameters with good precision.

#### Introduction

In the field of silicon solar cells, recent progress has been achieved in two directions: silicon heterojunctions and silicon nanowires. These two topics are briefly addressed here and we show some new characterization results that use conductive-probe atomic force microscopy (CP-AFM) measurements.

Silicon heterojunctions are formed between crystalline silicon (c-Si) and hydrogenated amorphous silicon (a-Si: H). Solar cell efficiencies of up to 23% have been demonstrated on high quality *n*-type *c*-Si wafers with layers of *p*-type *a*-Si:H deposited at the front (as the emitter) and *n*-type *a*-Si:H deposited at the back (as the back surface field), respectively [1]. Since transport properties are quite poor in *a*-Si:H due to the large amount of defects and band gap states and low carrier mobilities, the doped *a*-Si: H layers are used to form the junctions, but their thickness has to be kept very low. The front *a*-Si:H layer has to be very thin in order to minimize absorption of incoming photons and to privilege absorption in c-Si. One key feature of the Si heterojunctions is the very good passivation property of the c-Si surface by a-Si:H. This is even improved by inserting a thin undoped *a*-Si:H layer

\* Correspondence: jean-paul.kleider@lgep.supelec.fr

<sup>1</sup>Laboratoire de Génie Electrique de Paris, CNRS UMR 8507, SUPELEC, Univ P-Sud, UPMC Univ Paris 6, 11 rue Joliot-Curie, Plateau de Moulon, 91192 Gif-sur-Yvette Cedex, France.

#### **Experimental details**

#### Solar cell structure

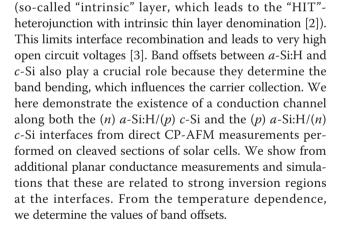

A typical solar cell structure based on *a*-Si:H/*c*-Si heterojunctions formed with *n*-type *c*-Si is presented in Figure 1. A similar structure stands for *p*-type *c*-Si, replacing the *n*-type *a*-Si:H by *p*-type *a*-Si:H and vice versa. For *n*-type *c*-Si, we used Float Zone, *n*-type *c*-Si wafers,  $\langle 100 \rangle$  oriented, with resistivity:  $\rho = 1-5 \Omega$  cm, and thickness:  $W = 300 \mu$ m. For the *p*-type *c*-Si, we used Czochralski (CZ) *c*-Si wafers,  $\langle 100 \rangle$  oriented, with resistivity:  $\rho = 14-22 \Omega$  cm, and thickness:  $W = 300 \mu$ m. We used indium tin oxide (ITO) as the front

<sup>© 2011</sup> Kleider et al; licensee Springer. This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/2.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Full list of author information is available at the end of the article

transparent conductive oxide (TCO), and aluminum as the back metal contact. The *a*-Si:H layers were deposited at Ecole Polytechnique in a radio frequency (13.56 MHz) plasma-enhanced chemical vapor deposition (PECVD) reactor at a substrate temperature of 200°C. Spectroscopic ellipsometry measurements and modeling were used to check that the deposited silicon thin layers were truly amorphous, and that no epitaxial growth occurred on the *c*-Si substrate.

#### CP-AFM

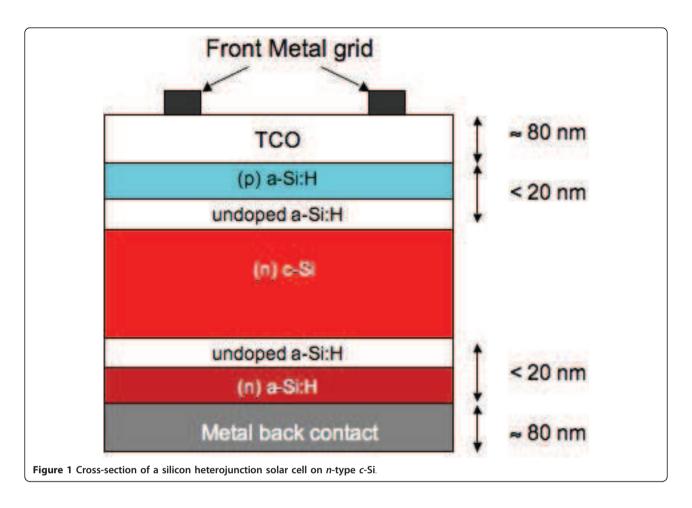

CP-AFM measurements were carried out using two different setups (i) in Ioffe Physical-technical Institute (NT-MDT Ntegra Aura) and (ii) in Laboratoire de Génie Électrique de Paris (Digital Instruments Nanoscope IIIa Multimode AFM with the RESISCOPE extension [4]). These setups allow one to apply a stable DC bias voltage to the device and to measure the resulting current flowing through the tip as the sample surface is scanned in contact mode. Schematic AFM setup is shown in Figure 2. In both measurements diamondcoated conductive probes made of silicon were used, the contact interaction force being in the range 100-500 nN. With the help of this technique one can simultaneously examine on the sample cleavages the surface topography and conductive properties of the layers constituting the solar cells. Note that, due to different softwares, the first setup provides images with current values (current flowing through the tip), while the second one provides resistance values, the resistance being defined as the ratio of the applied voltage to the measured current.

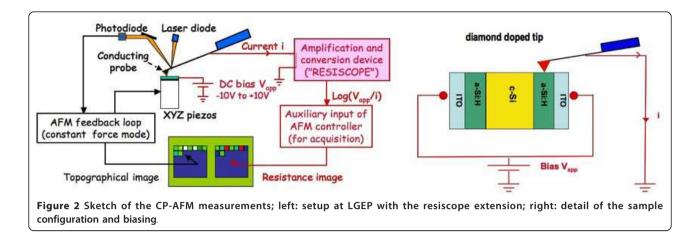

For these CP-AFM measurements, the normal solar cell structure was replaced by a simpler symmetric configuration, see Figure 3a, where the same *a*-Si:H layer was deposited on both sides of the *c*-Si wafer. Then ITO electrodes were deposited on top of both sides of the wafer, before the sample was cleaved. Some tests were also performed with aluminum instead of ITO as electrodes. The obtained CP-AFM results were globally the same. However, aluminum electrodes formed high ridges at the cleaved edge and their cross-section were poorly conductive due to strong oxidation of aluminum, what induced some problems in AFM imaging. Therefore, here we focus on samples with ITO on both sides. Thus, cleaved sections of ITO/(*n*) *a*-Si:H/(*p*) *c*-Si/ITO and ITO/(*p*) *a*-Si:H/(*n*) *c*-Si/ITO samples with different

thicknesses of the a-Si:H layer (20, 100, 300 nm) were investigated.

#### Planar conductance

The sample structure for these measurements is shown in Figure 3b for *p*-doped *a*-Si:H. The *a*-Si:H layer was deposited in the same run on both *n*-type *c*-Si and glass (Corning 1737). Top coplanar aluminum electrodes were then deposited on the top of *a*-Si:H. We measured the DC current, *I*, resulting from application of a DC bias, *V*, between two adjacent electrodes. We had several electrode designs with various gap distances between them. We checked that the current scaled with the inter-electrode gap distance. We also checked that the current was linearly dependent on the DC voltage, so that we defined the conductance G = I/V. This was then measured as a function of temperature between 150 and 300 K in a cryostat chamber pumped down to 10<sup>-5</sup> mbar.

The same kind of measurements were also performed on series of samples with n-doped a-Si:H deposited onto p-type c-Si and glass.

#### **Results and discussion**

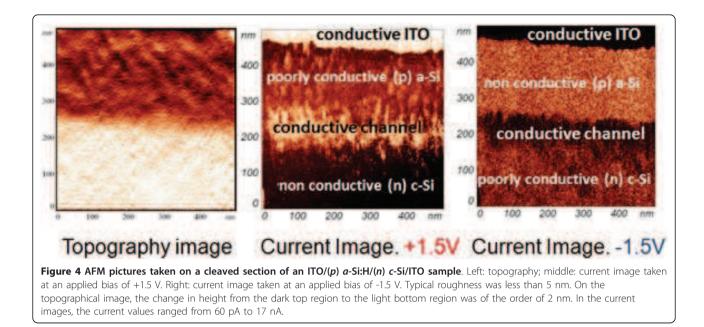

In Figure 4a,b,c, an example of topography and current images for two different biases, is presented for a (p) *a*-Si:H/(n) *c*-Si junction. At positive bias applied to the sample, conductive regions appear light in the current images, while for negative bias they appear dark. The current images clearly reveal a conductive interface layer between the c-Si substrate and the a-Si:H film. This layer is more conductive than both the *c*-Si and *a*-Si:H regions. This conductive interface layer was well observed on all samples for both (p) a-Si:H/(n) c-Si and (n) a-Si:H/(p) c-Si heterointerfaces whatever the a-Si:H layer thickness is. It is worth to note that the conductive layer is not an artifact that could come from the surface roughness. It can be clearly seen when current images are compared with the topography one. There exists one distinct boundary between the *a*-Si:H layer and *c*-Si wafer, and the detected conductive channel lies within c-Si substrate.

However, the quantitative results of the interface layer conductivity deduced from CP-AFM measurements

have to be considered carefully. Indeed, the reliability of the latter is affected by the quality and nature of the contact between the conductive tip and the sample surface. The sample surface roughness, the AFM tip radius, shape and pressure are well-known factors driving local electrical measurements. Moreover, surface states can induce additional band bending at the tip-surface junction modifying significantly the conductance values [5]. The CP-AFM scanning measurements can also be influenced by the oxidation process after cleaving the sample and the presence of a water meniscus between the tip and the surface that can also lead to tip-induced oxidation or trapping of carriers in localized states [6,7]. The contact between the tip and the cleaved surface can behave as a metal-oxide interface that then determines the current flowing through the tip.

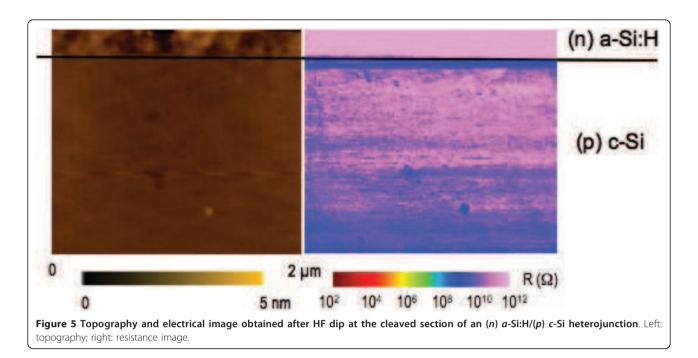

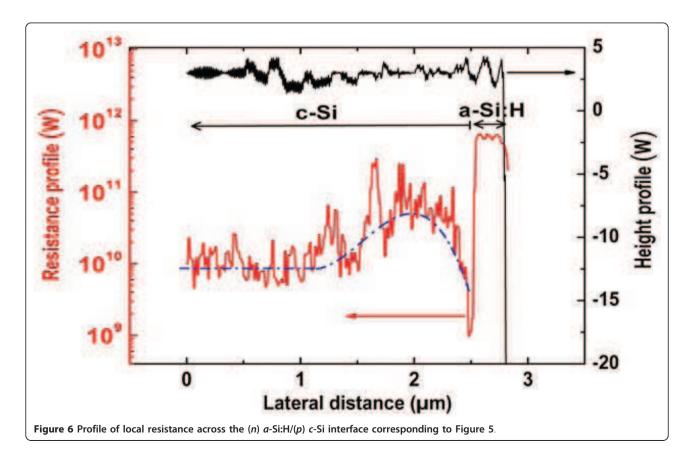

In order to minimize the effects of surface oxide and surface states, CP-AFM measurements were performed at LGEP under nitrogen atmosphere immediately after having dipped the sample in an HF solution. This treatment is known to passivate the silicon surface by reducing the density of silicon dangling bonds, thus minimizing the potential effect of surface states on the surface band bending. Figure 5 illustrates an example of topographical and electrical image of the cleaved section obtained under these conditions with, from top to bottom, the *n*-type *a*-Si:H layer (= 300 nm) and the *p*-type c-Si substrate. Contrary to Figure 4, the ITO contact is not observed since it has been partially removed after the HF dip. Compared to results of Figure 4, with the improved measurement procedure, a conductive channel at the (n) a-Si:H/(p) c-Si interface is even more clearly observed. The topographic and electrical profiles along the heterointerface presented on Figure 6 show a flat cleaved surface and a higher electrical contrast between the conductive channel and both the *a*-Si:H layer and the *c*-Si substrate. In addition, the electrical image in the *c*-Si also shows a region with increasing conductivity of about 1  $\mu$ m width when sweeping away from the *a*-Si:H/*c*-Si interface. This can be linked to the depleted space charge region in the low-doped (*p*) *c*-Si ( $N_a < 10^{15}$  cm<sup>-3</sup>), which has a width close to 1  $\mu$ m.

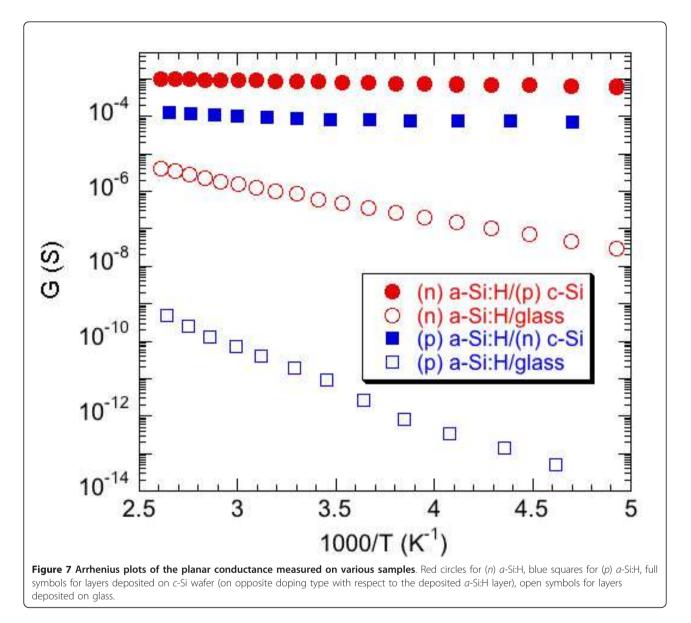

The existence of an interface conductive channel has also been evidenced by the planar conductance measurements. Indeed, it was shown that the planar conductance was orders of magnitude larger for the samples deposited on *c*-Si substrates (both *n*- and *p*-type) than that measured on the a-Si:H layer deposited in the same run on glass substrates. Activation energy of the conductance for the samples deposited on glass was found equal to about 0.35 and 0.2 eV for the (p) *a*-Si:H and (*n*) a-Si:H layers, respectively [8,9]. These are typical values for doped *a*-Si:H. The conductance for samples deposited on *c*-Si had much lower activation energy, as can be seen in Figure 7. This high planar conductance measured on the samples deposited on *c*-Si is in very good agreement with the presence of the conducting channel revealed by our CP-AFM measurements.

We attribute this thin conductive interface channel along with the low conductance activation energy to a strong inversion layer at the *c*-Si surface that is related to the band offset at the heterojunction.

In order to further demonstrate the existence of the strong interface inversion layer and the related contribution to the conductance, we used the AFORS-HET software [10] to evaluate the free carrier profiles. We

introduced the density of states (DOS) typical for *n*-type *a*-Si:H (band gap  $E_{\rm g} = 1.75$  eV) consisting of two exponential band tails with characteristic energies  $k_{\rm B}T_{\rm C}$  and  $k_{\rm B}T_{\rm V}$  of 0.055 and 0.12 eV for the conduction and valence band, respectively, and with a pre-exponential

factor of  $2 \times 10^{21}$  cm<sup>-3</sup> eV<sup>-1</sup>, and two Gaussian deep defect distributions of donor and acceptor nature being located at 0.58 and 0.78 eV above the top of the valence band, respectively, with a maximum value of  $8.7 \times 10^{19}$  cm<sup>-3</sup> eV<sup>-1</sup> and a standard deviation of 0.23 eV. A doping

density of  $N_{\rm d} = 5.34 \times 10^{19}$  cm<sup>-3</sup> was also introduced, setting the Fermi level  $E_{\rm F}$  at 0.2 eV below the conduction band at 300 K, as suggested from the activation energy of the conductance data measured on (*n*) *a*-Si:H samples deposited on glass. The doping density in the crystalline silicon was set at  $N_{\rm a} = 7 \times 10^{14}$  cm<sup>-3</sup>, as found from capacitance versus bias measurements [11], and in agreement with the resistivity of our CZ *c*-Si *p*-type wafers.

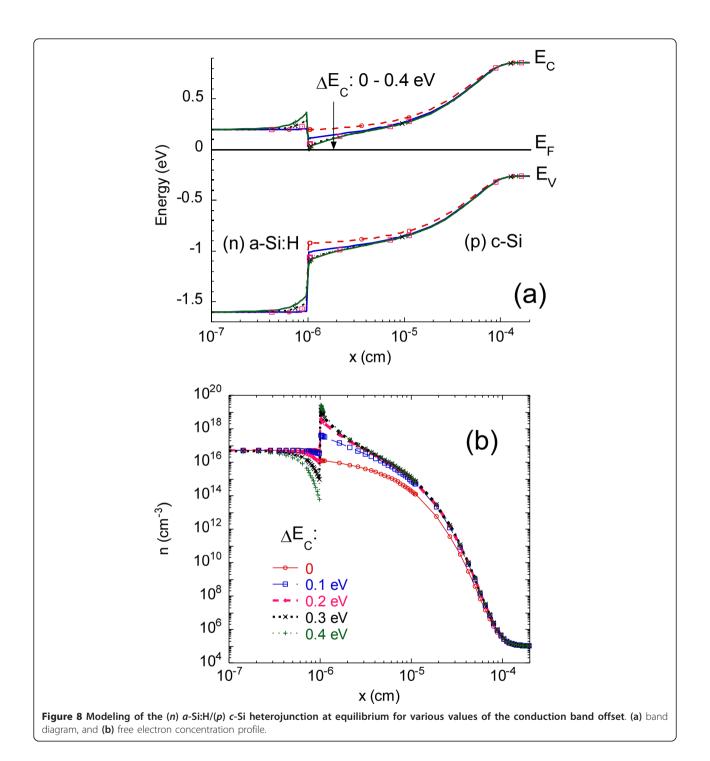

Figure 8a,b shows the calculated band diagram and the electron concentration profile for various values of the conduction band offset  $\Delta E_C = E_C^{a-\text{Si:H}} - E_C^{c-\text{Si}}$ , respectively. An inversion layer is indeed clearly seen in the interface region of *c*-Si when sticking increase of electron concentration with  $\Delta E_C$  is observed. On the contrary, increasing  $\Delta E_C$  leads to a stronger electron depletion in (n) *a*-Si:H close to the interface due to a stronger band bending.

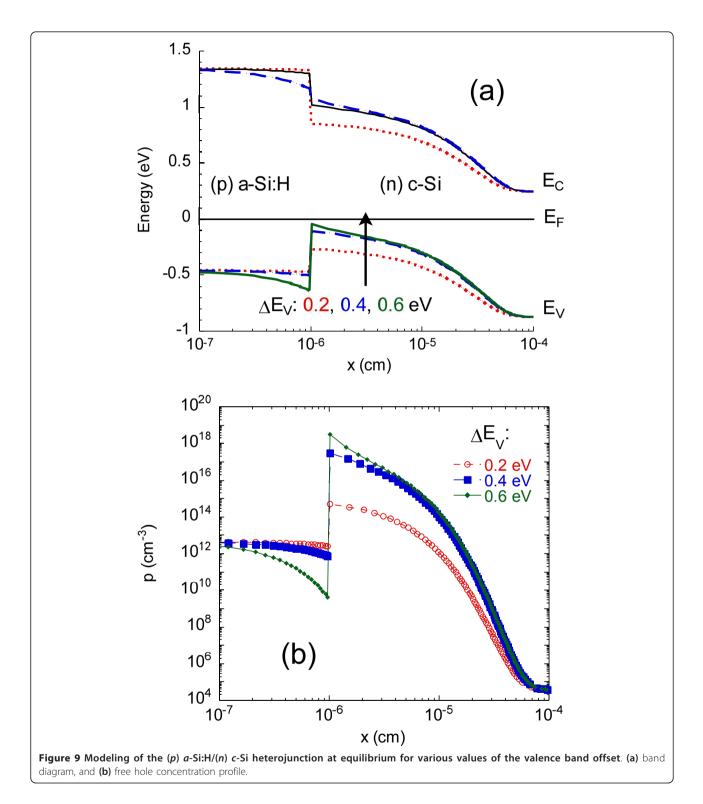

Similar simulations were performed for the (*p*) *a*-Si:H/ (*n*) *c*-Si heterojunction. The band gap of *a*-Si:H also was taken at  $E_{\rm g} = 1.75$  eV, and the position of the Fermi level was fixed at 0.45 eV, which is a reasonable value for *p*-type *a*-Si:H, in agreement with our conductivity measurements. After having introduced the *a*-Si:H parameters, we combined the *a*-Si:H layer with an *n*-type *c*-Si substrate with  $N_{\rm d} = 2 \times 10^{15}$  cm<sup>-3</sup> (corresponding to the resistivity value) to simulate the (*p*) *a*-Si:H/(*n*) *c*-Si heterojunction. Calculated band diagram and evaluated hole concentration profiles for different values of valence band offset  $\Delta E_{\rm V} = E_{\rm V}^{c-{\rm Si}} - E_{\rm V}^{a-{\rm Si}:{\rm H}}$  are shown in Figure 9a,b, respectively. Drastic increase of hole concentration is observed in (*n*) *c*-Si layer near the interface

for increasing values of band offset, with the appearance of a strong inversion layer for  $\Delta E_V > 0.2$  eV. Thus, simulations of both (*n*) *a*-Si:H/(*p*) *c*-Si and (*p*) *a*-Si:H/ (*n*) *c*-Si heterojunctions show the appearance of a strong inversion interface region above a given value of band offset. The planar conductance can be related to the carrier density profile. Indeed, the conductance of the strong inversion channel can be written

$$G = \frac{qh}{L}\,\mu N,\tag{1}$$

where q is the elementary charge, h the length of the coplanar electrodes, L the gap between them,  $\mu$  the mobility of the carriers in the strong inversion region, and N the sheet carrier density, i.e., the integral over the *c*-Si thickness of the carrier concentration. Carriers to

be considered are the electrons for the (n) *a*-Si:H/(p) *c*-Si interface and the holes for the (p) *a*-Si:H/(n) *c*-Si interface. We calculated the values of *N* as a function of the band offset and of the temperature. We thus were able to compute the planar conductance and compare it

to the experimental data. This proved to be a very precise way to determine the band offsets in the (*n*) *a*-Si:H/ (*p*) *c*-Si system [12], where a value of  $\Delta E_C = 0.15$  eV was found. In the (*p*) *a*-Si:H/(*n*) *c*-Si system, the measured resistance profile was compared to the calculated resistivity profile across the heterojunction. Both profiles have very similar shapes, and the thickness of the strong inversion layer is of the same order of magnitude (50-100 nm). Further analysis of the CP-AFM measurements shows that a strong inversion layer only exists if the valence band offset is large enough,  $\Delta E_V > 0.25$  eV [13]. A more detailed theoretical and modeling study including the effect of temperature dependence of the band gaps and of the DOS parameters in *a*-Si:H is under way. It confirms our previous determination of conduction band offset and indicates that the value of valence band offset that best reproduces our experimental data is around  $\Delta E_V = 0.4$  eV.

#### Conclusion

Silicon heterojunctions were characterized by the CP-AFM technique. A conductive channel between *a*-Si:H layer and *c*-Si substrate was detected in both (*n*) *a*-Si:H/ (*p*) *c*-Si and (*p*) *a*-Si:H/(*n*) *c*-Si heterostructures. This conductive channel was attributed to the existence of a strong inversion layer that was also suggested by planar conductance measurements. The existence of this layer can be explained by relatively large band offsets at the heterojunction, as we demonstrated by numerical calculations of the carrier concentration profiles. Comparison with our experimental data allowed us to deduce values of the conduction and valence band offsets.

#### Abbreviations

CP-AFM: conductive-probe atomic force microscopy; CZ: Czochralski; DOS: density of states; ITO: indium tin oxide; PECVD: plasma-enhanced chemical vapor deposition; TCO: transparent conductive oxide.

#### Acknowledgements

This study was partly supported by European Community's Seventh Framework Programme (FP7/2007-2013) under Grant agreement no. 211821 (HETSI project), by OSEO's Solar Nanocrystal project as well as by CNRS and the Russian Foundation for Basic Research in the framework of a joint Russian-French project (07-08-92163), and by the Programme of Fundamental Research of Russian Academy of Sciences (Programme No. 27). Two of the authors, W. Favre and O.A. Maslova, would like to thank ADEME and SUPELEC, and the French embassy in Russia, respectively, for their grants.

#### Author details

<sup>1</sup>Laboratoire de Génie Electrique de Paris, CNRS UMR 8507, SUPELEC, Univ P-Sud, UPMC Univ Paris 6, 11 rue Joliot-Curie, Plateau de Moulon, 91192 Gif-sur-Yvette Cedex, France. <sup>2</sup>A.F. Ioffe Physico-Technical Institute, Polytechnicheskaya Str. 26, St. Petersburg, 194021, Russia. <sup>3</sup>St. Petersburg Academic University-Nanotechnology Research and Education Centre RAS, Hlopina Str. 8/3, St. Petersburg, 194021, Russia. <sup>4</sup>Laboratoire de Physique des Interfaces et des Couches Minces, Ecole Polytechnique, CNRS, 91128 Palaiseau, France. <sup>5</sup>TOTAL S.A., Gas & Power-R&D Division, Courbevoie, France.

#### Authors' contributions

PRIC and ML deposited the samples. JA, AVA, and EVG carried out CP-AFM measurements. WF carried out planar conductance measurements. ASG and OAM performed modeling. MEGF and EIT participated in the analysis and guidance of the study. JPK supervised the study, participated in the analysis

of the results, and drafted the manuscript. All authors read and approved the manuscript.

#### **Competing interests**

The authors declare that they have no competing interests.

Received: 6 September 2010 Accepted: 16 February 2011 Published: 16 February 2011

#### References

- Mishima T, Taguchi M, Sakata H, Maruyama E: Development status of high-efficiency HIT solar cells. Sol Energy Mater Sol Cells 2011, 95:18.

- Tanaka M, Taguchi M, Matsuyama T, Sawada T, Tsuda S, Nakano S, Hanafusa H, Kuwano Y: Development of New a-Si/c-Si Heterojunction Solar Cells: ACJ-HIT (Artificially Constructed Junction-Heterojunction with Intrinsic Thin-Layer). Jpn J Appl Phys 1992, 31:3518.

- Taguchi M, Tsunomura Y, Inoue H, Taira S, Nakashima T, Baba T, Sakata H, Maruyama E: High efficiency HIT solar cell on thin (< 100 μm) silicon wafer. Proceedings of the 24th EPVSEC; Hamburg, Germany 2009, 1690-1693.

- Houze F, Schneegans O, Boyer L: Imaging the local electrical properties of metal surfaces by atomic force microscopy with conducting probes. *Appl Phys Lett* 1996, 69:1975.

- Eyben P, Vandervorst W, Alvarez D, Xu M, Fouchier M: Probing Semiconductor Technology and Devices with Scanning Spreading Resistance Microscopy. In Scanning Probe Microscopy. Edited by: Kalinin S, Gruverman A. New York: Springer; 2007:31-88.

- Kleider JP, Longeaud C, Bruggemann R, Houze F: Electronic and topographic properties of amorphous and microcrystalline silicon thin films. *Thin Solid Films* 2001, 383:57.

- Rezek B, Mates T, Sipek E, Stuchlik J, Fejfar A, Kocka J: Influence of combined AFM/current measurement on local electronic properties of silicon thin films. J Non-Cryst Solids 2002, 299-302:360.

- Kleider JP, Soro YM, Chouffot R, Gudovskikh AS, Rocai Cabarrocas P, Damon-Lacoste J, Eon D, Ribeyron P-J: High interfacial conductivity at amorphous silicon/crystalline silicon heterojunctions. J Non-Cryst Solids 2008, 354:2641.

- Favre W, Labrune M, Dadouche F, Gudovskikh AS, Rocai Cabarrocas P, Kleider JP: Study of the interfacial properties of amorphous silicon/n-type crystalline silicon heterojunction through static planar conductance measurements. *Phys Status Solidi C* 2010, 7:1037.

- Stangl R, Kriegel M, Schmidt M: AFORS-HET, Version 2.2, a numerical computer program for simulation of heterojunction solar cells and measurements. Proceedings of the 4th World Conference on Photovoltaic Energy Conversion; Hawaii, USA 2006, 1350-1353.

- Gudovskikh AS, Ibrahim S, Kleider JP, Damon-Lacoste J, Rocai Cabarrocas P, Veschetti Y, Ribeyron PJ: Determination of band offsets in a-Si:H/c-Si heterojunctions from capacitance-voltage measurements: Capabilities and limits. *Thin Solid Films* 2007, 515:7481.

- Kleider JP, Gudovskikh AS, Rocai Cabarrocas P: Determination of the conduction band offset between hydrogenated amorphous silicon and crystalline silicon from surface inversion layer conductance measurements. *Appl Phys Lett* 2008, **92**:162101.

- Maslova OA, Alvarez J, Gushina EV, Favre W, Gueunier-Farret ME, Gudovskikh AS, Ankudinov AV, Terukov EI, Kleider JP: Observation by conductive-probe atomic force microscopy of strongly inverted surface layers at the hydrogenated amorphous silicon/crystalline silicon heterojunctions. *Appl Phys Lett* 2008, 97:252110.

#### doi:10.1186/1556-276X-6-152

Cite this article as: Kleider *et al.*: Characterization of silicon heterojunctions for solar cells. *Nanoscale Research Letters* 2011 6:152.